## **Acousto-Optic Modulator Driver**

**Including: Modulator Alignment**

M1431-aQ80-9

**CAUTION**

**OPERATE BELOW MAXIMUM DUTY CYCLE OF AO MODULATOR**

Refer to AOM data sheet for limits.

### **Instruction Manual**

# RFA681 Series Analog Modulation, 80MHz Amplifier Remote I2C Power Level Control

Models -

RFA681-xxx : 80MHz, 120W output, 0-10V modulation

Options -xxx, combinations possible.

- D : TTL digital (On-Off) modulation

- DA : dual analog and TTL digital modulation

- BR : Brass water cooled heatsink (water fittings on rear face only)

ISOMET (UK) Ltd, 18 Llantarnam Park, Cwmbran, Torfaen, NP44 3AX, UK. Tel: +44 1633-872721, Fax: +44 1633 874678, e-mail: <a href="mailto:sales-uk@isomet.com">sales-uk@isomet.com</a>

#### 1. GENERAL

#### Key Features:

- 24Vdc, water cooled high power amplifier.

- Peak RF output >130W at 80.00MHz

- RF rise/fall time < 400/100nsec at 180W

- High Speed amplitude modulation RFA681: analog RFA681D: TTL digital RFA681DA: analog & TTL digital

- Modulation peak level is defined by two methods.

- Digitally programmed potentiometer stack

- Manual adjustment potentiometer.

- Digital potentiometer programmed via buffered I2C interface.

- Opto-isolated PLC compatible inputs on POT select and RF enable inputs. (Response time circa 1msec).

- Tri colour LED status indicator.

- High VSWR shut-down protection.

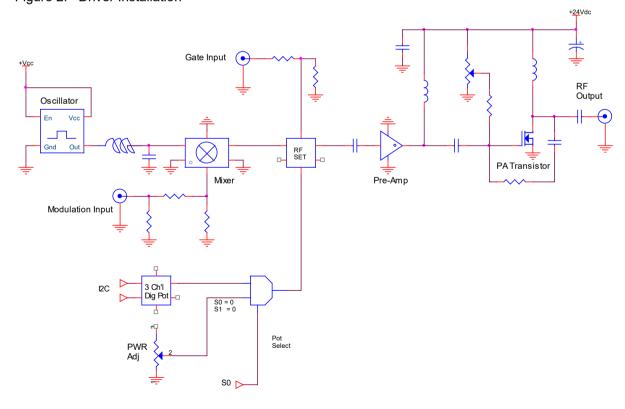

A block diagram of the driver is shown in Figure 3. The center frequency is determined by free-running quartz-crystal oscillator. The frequency is accurate and stable to within  $\pm\,$  25ppm. A high-frequency, diode ring modulator provides high speed amplitude modulation of the RF carrier. The peak RF power level is set by a multi-turn manual potentiometer or by digitally controlled potentiometer.

#### 2, <u>CONTROL</u>

Two inputs directly control the RF output; Gate and Modulation.

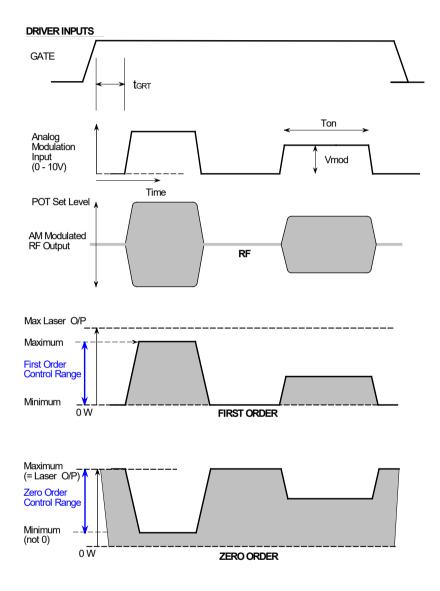

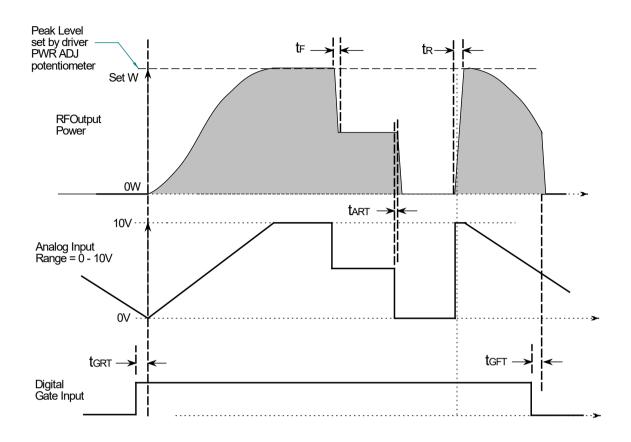

The relationship between the driver control inputs, the RF waveform and AO response is shown below for RFA681 driver with analog modulation.

Figure 1: Typical Analog Modulation Waveforms

#### **Timing Specifications**

| ldent        | Description                                                                      | Max    |

|--------------|----------------------------------------------------------------------------------|--------|

| <b>t</b> R   | RF rise time resulting from 'large signal' analog modulation                     | 250 ns |

| <b>t</b> R   | RF rise time resulting from TTL modulation (Option –DA)                          | 300 ns |

| tF           | RF fall time resulting from 'large signal' analog or TTL: modulation             | 100 ns |

| <b>t</b> art | Delay between a change in Modulation input and the resultant change in RF output | 250 ns |

| <b>t</b> GRT | Delay between a change in digital Gate input and RF fully enabled                | 0.5 ms |

| <b>t</b> GFT | Delay between a change in digital Gate input and RF fully disabled               | 2.5 ms |

#### Signal description

#### **Gate** (active high enables the RF amplifier)

PLC compatible opto-isolated input

Default condition is RF Off.

A high level (5V < V < 24V) will gate the RF **ON**.

A low level (0V < V < 4V), or not connected will gate the RF  $\underline{\text{OFF.}}$

#### **Modulation** (Analog 0 - 10V)

Provides high speed proportional amplitude control of the RF output.

Lower limit: an input voltage of less than 0.4V will drive the RF Off.

Upper limit: an input of 10V will result in the maximum RF output,

(For RFA681D type, modulation control is On:Off and requires a 5V CMOS / TTL compatible input).

The amplitude level is defined by the selected RF power adjustment POT.

# Modulation duty cycle needs to be adjusted according to the average Rf power limitation of the AOM

#### RF Power Adjustment (POT set level)

The maximum RF power limit is set by one of two methods. The method is selectable by the user.

a) A manual multi-turn potentiometer 'PWR ADJ'

Maximum RF power = fully clockwise

or

b) A quad 256 step digital potentiometer configured to give independent power control with variable end limits

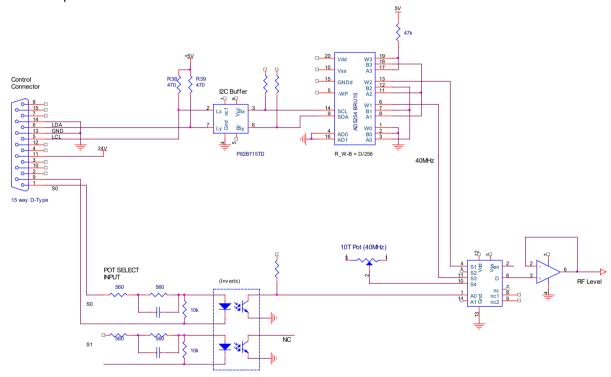

Three channels are used for power level control. RDAC0, RDAC1, and RDAC3 (see AD5254 data sheet). Levels are set remotely via an I2C compatible serial connection. The slave address for the digital I2C potentiometer is at 0101100. (AD0 = AD1 = 0)

#### **DC Power**

A low impedance DC power supply is required. The operating voltage is +24Vdc only at a current drain of approximately < 14A. The external power source should be regulated to  $\pm$  2% and the power supply ripple voltage should be less than 200mV for best results. Higher RF output power is achieved at 28Vdc.

#### 2.1 Thermal Interlocks

The AOM and Driver are fitted with thermostatic switches which will switch open circuit if a predetermined temperature is exceeded. These thermal interlocks will reset once the AO device and / or RF driver are cooled below this temperature.

- The driver thermal switch over-temperature threshold is 50deg C

- The M1431 series thermal switch over-temperature threshold is 40deg C

The hysteresis of the thermal switches is 7-10deg C.

Once in a fault state the coolant temperature will need to be reduced to reset the thermal switches.

#### **Precautions**

Analog levels must not exceed 15 volts positive, or -0.5 volts negative.

PLC logic input levels must not exceed 24 volts

Water cooling is mandatory.

The heatsink temperature must not exceed 70°C.

Corrosion inhibitor should be added to the cooling water

SERIOUS DAMAGE TO THE AMPLIFIER MAY RESULT IF THE TEMPERATURE EXCEEDS 70°C. SERIOUS DAMAGE TO THE AMPLIFIER MAY ALSO RESULT IF THE RF OUTPUT CONNECTOR IS OPERATED OPEN-CIRCUITED OR SHORT-CIRCUITED.

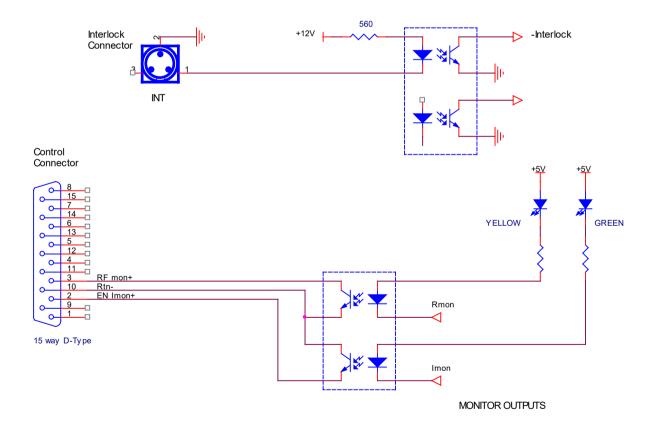

#### 2.2 **LED Indicator and Monitor outputs**

The front panel tri-colour LED indicates the operating state.

(RF PWR ADJ)

80MHz LED

#### **RED**

The top LED will illuminate RED when there is a poor VSWR load (High reflected RF power fault).

#### Normal condition is OFF

A fault signal is triggered when the reflected RF power exceeds approximately 50% of the average forward power for more than 1 second. This fault is latching and the driver is disabled (RF power will go to zero). This fault can occur if the RF connection between the AOM and driver is broken.

#### Resetting

Once the fault condition is corrected, it will be necessary to reset the driver.

1) Turn the DC power OFF and ON

or

2) Press momentary RESET button on driver located to right to the D-type

#### **YELLOW**

The middle LED will illuminate YELLOW, when the RF outputs are live and provided that

- a) the Gate duty cycle is more than 20% (approx).

- b) the RF average power is > 30W (approx)

Normal condition is ON, but may be OFF if the above conditions are not met

#### **GREEN**

The lower LED will illuminate GREEN when the following signals are all true:

- 1) RF DC power is applied and

- 2) Interlocks are valid and

- 3) GATE input is high.

#### Normal condition is ON

#### LEDS Off

The GREEN and/or YELLOW LED's will not illuminate if:

- a) the internal driver thermal interlock switch is open (Over temperature fault)

- b) the AOM thermal interlocks switch is open (Over temperature fault)

- c) the AOM thermal interlock is not connected to the driver interlock input

- d) the DC supply is off.

The RED LED should be OFF

#### **Monitor Outputs**

The status of the YELLOW and GREEN LEDS is available at the D-type connector These outputs are opto-isolated .

"Enabled" = low impedance between pins 2 and 10 = Green LED ON

"RF Active" = low impedance between pins 3 and 10 = Yellow LED ON

#### 3. INSTALLATION AND ADJUSTMENT

The basic set-up below is described using the manual RF power limit adjustment.

The remote power adjustment is described from 3.15 onwards. The driver will default to manual adjustment unless the remote power adjustment is selected,

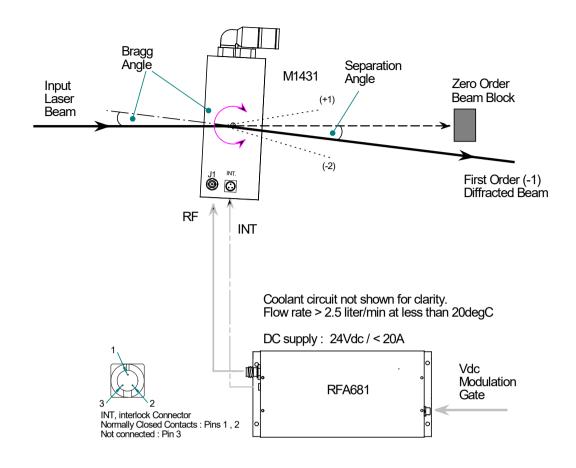

3.1 Connect cooling water to the RFA681

Connect cooling water to the AO device.

Refer to Figure 2. Use of a Corrosion inhibitor is strongly advised.

<u>Due to the high RF power dissipated in the AO modulator, it is paramount that the device is operated only when water cooling is circulating.</u>

For optimum AO performance ensure the flow rate is more than 2 litres/minute at < 20 deg.C

3.2 Connect the + 24V (or +28V) DC supply (See page 15).

DO NOT turn on DC supply until step 3.8.

- 3.3 Connect the TNC output RF connector to the acousto-optic modulator TNC RF input (or a  $50\Omega$  RF load, if it is desired to measure the RF output power).

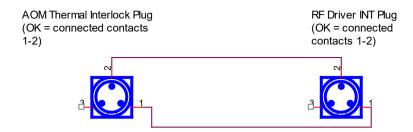

- 3.4 Connect the <u>Interlock</u> of the acousto-optic modulator (mini 3-pin snap connector) to the RF driver "INT" input (mini 3-pin snap connector). Connect pin1 to pin1 and pin2 to pin2.

If the temperature of the modulator exceeds 40°C or the internal driver temperature exceeds 50°C then the interlock connection becomes open circuit, disabling the RF output. An LED indicator illuminates when the Interlocks are closed and the RF is enabled. In addition, a open drain 'interlock valid' signal output is provided on pin 2 of the D-type connector for remote monitoring purposes.

3.5 Adjustment of the RF output power is best done with amplifier connected to the acousto-optic modulator. When shipped, the Amplifier maximum output power is set to approx' 100W selecting the manual PWR ADJ pot and 120W for the digital pots.

The optimum RF power level required for the modulator to produce maximum first order intensity will be differ depending in the laser wavelength. Applying RF power in excess of this optimum level will cause a decrease in first order intensity (a false indication of insufficient RF power) and makes accurate Bragg alignment difficult. It is therefore recommended that initial alignment be performed at a low RF power level.

- 3.6 Locate the PWR ADJ on the driver end plate.

The 80MHz RF Power adjuster is adjacent to the LED stack

- 3.7 With an insulated alignment tool or screwdriver rotate the PWR ADJ potentiometer fully anticlockwise (CCW) i.e. OFF, then clockwise (CW) approx 5 turns.

- 3.8 Ensure cooling water is connected and flowing. Apply DC to the amplifier.

- 3.9 Apply a 10% On / 90% Off duty cycled 10V peak signal to the modulation input, pin4.

#### DO NOT EXCEED AVERAGE POWER LIMITATION OF AOM

(Average power = peak power x duty cycle)

Connect pin 4 of 'D' to the signal and pin 12 of 'D' to the signal return (0V).

- For RFA681-D, apply a duty cycled TTL=H to pin 4

- For RFA681-DA, also apply a TTL=H to pin 7

- 3.10 Apply a constant PLC <u>high</u> level (typically 12V or 24V) to the digital gate input on the D-type connector. Connect pin 8 of the 'D' to the Signal and pin 15 of the 'D' to the signal return.

- 3.11 Apply a constant PLC <u>low</u> level (less than 2V) to the POT SELECT input (S0) on the D-type. (alternatively, do not connect if remote RF power adjustment is not required)

Connect pin 1 of the 'D' to the Signal and pin 9 of the 'D' to the signal return.

A low level (or no connect) will enable power adjustment using the Manual pots.

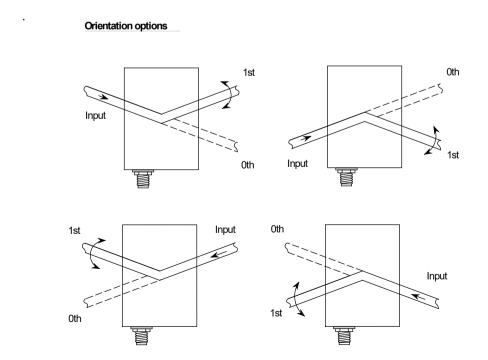

Input the laser beam toward the centre of either aperture of the AOM. Ensure the polarization is horizontal with respect to the base and the beam height does not exceed the active aperture height of the AOM. Start with the laser beam normal to the input optical face of the AOM and very slowly rotate the AOM (either direction). See Figure 4 for one possible configuration.

- 3.12 Observe the diffracted first-order output from the acousto-optic modulator and the undeflected zeroth order beam. Adjust the Bragg angle (rotate the modulator) to maximise first order beam intensity with the 80MHz Frequency selected.

- 3.13 After Bragg angle has been optimized, slowly increase the RF power by turning PWR ADJ clockwise until maximum first order intensity is obtained.

#### DO NOT EXCEED AVERAGE POWER LIMITATION OF AOM

(Average power = peak power x duty cycle)

#### 3.15 Remote RF Power Adjust

The RF power may be adjusted remotely using an I2C compatible interface. The control circuit is based on the Analog Devices non-volatile 256 step digital potentiometer AD5254. The accompanying data sheet describes the communication protocol.

The slave address for the digital I2C potentiometer is at 0101100. (AD0 = AD1 = 0) Maximum resistance equates to maximum RF power.

The digital potentiometer value is non-volatile and will recall the last saved value on powerup.

DO NOT exceed +5V on the I2C Inputs, LDA (data IO) and LCL (clock)

The I2C signals are buffered using the bus extender chip P82B715 from NXP

To enable remote RF power control, connect pin 1 (S0) of the 15way D-type control driver connector to a PLC compatible logic port and apply a high signal.

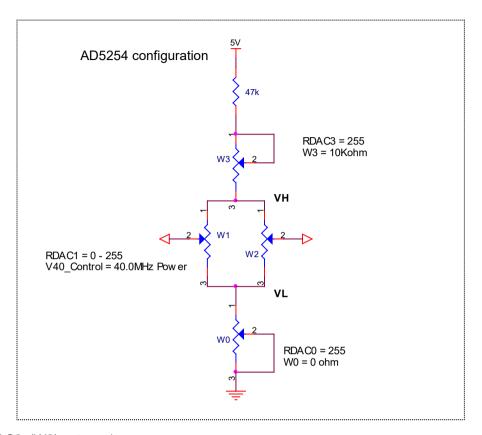

The four digital pots are configured into a potential divider.

The main power control pot W1 is in parallel with W2 and thus equates to 5Kohm resistance.

The upper and lower limit adjustment Pots W3 and W0 apply to both W1 and W2.

RDAC2 (W2) not used

RDAC1 defines the 80 MHz power control factor. (shown 40MHz in diagram above). V40\_Control = VL + (VH-VL) x W1/255 where W1= 8-bit value programmed into RDAC1

RDAC0 defines the lower limit pot

Lower pot resistance R\_W0 = (255-W0)/255 x 10Kohm

Lower limit voltage VL = (R\_W0) / (47K+R\_W3+5K+R\_W0)

RDAC3 defines the upper limit pot

Upper pot resistance R\_W3 = (W3)/255 x 10Kohm

Upper limit voltage VH = (R\_W0+5K) / (47K+R\_W3+5K+R\_W0)

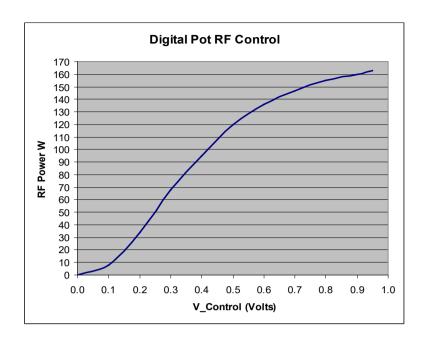

The full range power adjustment is shown below. Settings: RDAC3 =  $0 (R_W3=0k)$  and RDAC0 =  $255 (R_W0=0k)$ . The V\_Control scale equates to 0-255 adjustment range on RDAC1 (W1)

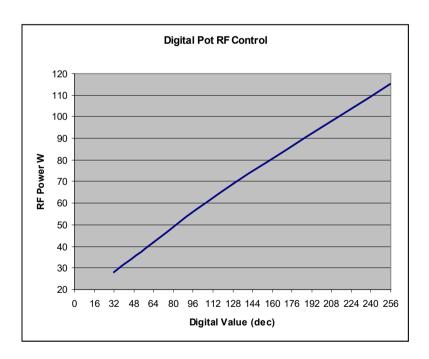

By adjusting the values of RDAC0 and RDAC3 it is possible to increase the adjustment resolution of the 8-bit power level control at 80.0 MHz (RDAC1) over a defined range.

A typical Digital Power curve is shown below. In this case settings are: RDAC3 = 255 (R\_W3=10k) and RDAC0 = t 200 (R\_W0=2K)

#### 4. <u>MAINTENANCE</u>

#### 4.1 Cleaning

It is of utmost importance that the optical apertures of the deflector optical head be kept clean and free of contamination. When the device is not in use, the apertures may be protected by a covering of masking tape. When in use, frequently clean the apertures with a pressurized jet of filtered, dry air.

It will probably be necessary in time to wipe the coated window surfaces of atmospherically deposited films. Although the coatings are hard and durable, care must be taken to avoid gouging of the surface and leaving residues. It is suggested that the coatings be wiped with a soft ball of brushed (short fibres removed) cotton, slightly moistened with clean alcohol. Before the alcohol has had time to dry on the surface, wipe again with dry cotton in a smooth, continuous stroke. Examine the surface for residue and, if necessary, repeat the cleaning.

#### 4.2 Troubleshooting

No troubleshooting procedures are proposed other than a check of alignment and operating procedure. If difficulties arise, take note of the symptoms and contact the manufacturer.

#### 4.3 Repairs

In the event of deflector malfunction, discontinue operation and immediately contact the manufacturer or his representative. Due to the high sensitive of tuning procedures and the possible damage which may result, no user repairs are allowed. Evidence that an attempt has been made to open the optical head will void the manufacturer's warranty.

#### **RFA681 Connection Summary**

1.0 15 way 'D' Type Control Connection

> Signal (see notes) Pin out connection **Type**

**NECESSARY**

(All driver options)

**Digital Gate** Input Signal pin 8 PLC high (5v < V < 24v) = ONReturn pin 15

PLC low (0.0v < V < 4v) or NC = OFF

RFA681 and RFA681-DA

**Analogue Modulation** Input Signal pin 4 < 0.4V(off) to 10.0V(on) Return pin 12

- or -

Option -D RFA681-D

**Digital Modulation** Signal pin 4 Input TTL high (2.7v < V < 5.0v) = ONReturn pin 12

TTL low (0.0v < V < 0.8v) = OFF

- and -

Option -DA only RFA681**-DA**

**Digital Modulation** Input Signal pin 7 TTL high (2.7v < V < 5.0v) = ONReturn pin 14

TTL low (0.0v < V < 0.8v) = OFF

Interlock \*\*\* Connect to AOM "INT" Input

Normally closed

**OPTIONAL**

'Enabled' monitor Output Signal pin 2 Return pin 10

(Open collector logic, Low = OK) Maximum applied voltage

(via external pull up resistor) = 24V

Maximum current = 20mA

'RF Status' monitor Output Signal pin 3 Return pin 10

(Open collector logic, Low = OK) Maximum applied voltage

(via external pull up resistor) = 24V

Maximum current = 20mA

I2C Clock Input Signal pin 5

(0.0v < V < 5.0v)Return pin 13

I2C Data IO In/Out Signal pin 6

Return pin 13 (0.0v < V < 5.0v)

POT Select Control, S0 Signal pin 1 Input PLC high (5v<V<24v) = Digital Pot Return pin 9

PLC low (0.0v<V<4v) or NC = Manual Adjust

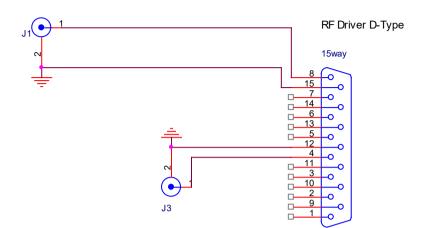

#### RFA681 (Analog Modulation) input connections

J1 = Digital GATE / RF Enable input PLC compatible Logic HIGH (5V < V < 24V) = ON Logic LOW (0V < V < 4V) = OFF

J3 = ANALOG MODULATION input 0V (off) - 10V( max on)

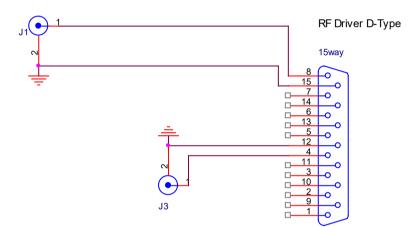

#### RFA681-D (Digital Modulation) input connections

J1 = Digital GATE / RF Enable input PLC compatible Logic HIGH (5V < V < 24V) = ON Logic LOW (0V < V < 4V) = OFF

J3 = DIGITAL MODULATION input TTL compatible levels Logic HIGH (2.7V < V < 5V) = On Logic LOW (0V < V < 0.8V) = Off

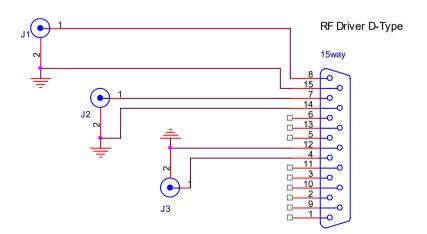

#### RFA681-DA (Dual Modulation) input connections

J1 = Digital GATE / RF Enable input PLC compatible Logic HIGH (5V < V < 24V) = ON Logic LOW (0V < V < 4V) = OFF

J2 = DIGITAL MODULATION input TTL compatible levels Logic HIGH (2.7V < V < 5V) = On Logic LOW (0V < V < 0.8V) = Off

J3 = ANALOG MODULATION input 0V (off) - 10V( max on)

#### Interlock connection

DC supply connection for drivers fitted with solder type feed-through.

Case stud = 0V

#### Notes:

\*\*\* The interlock signal must be connected. Contacts closed for normal operation.

#### 2.0 Mounting Holes: 4 off M5

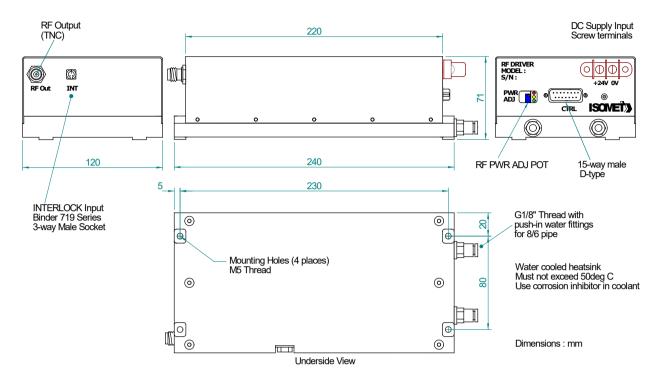

Figure 2: Driver Installation

Figure 3: Driver Block Diagram

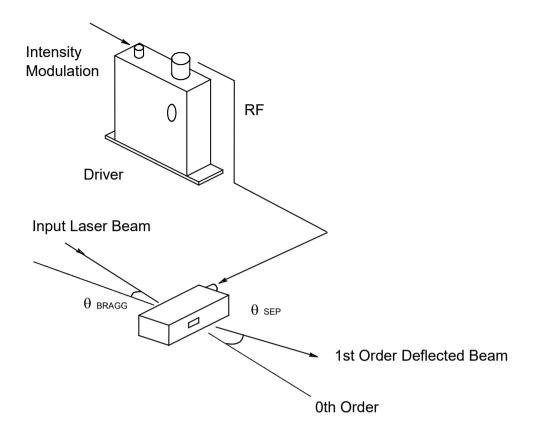

Figure 4: Typical Connection Configuration using RFA681 series.

#### **Basic AO Modulator Parameters**

The input Bragg angle, relative to a normal to the optical surface and in the plane of deflection is:

$$\theta$$

BRAGG =  $\frac{\lambda.fc}{2.v}$

The separation angle between the Zeroth order and the First order is:

$$\theta \text{ SEP} = \frac{\lambda . fc}{v}$$

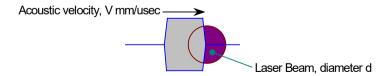

Optical rise time for a Gaussian input beam is approximately:

where:  $\lambda$  = wavelength

fc = centre frequency = 80MHz (see AOM data sheet)

v = acoustic velocity of interaction material = 5.7mm/usec (aQ)

$d = 1/e^2$  beam diameter

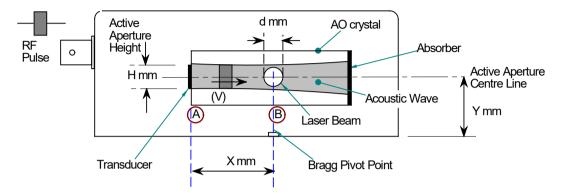

Figure 5. Modulation System

#### Appendix A: Beam Position

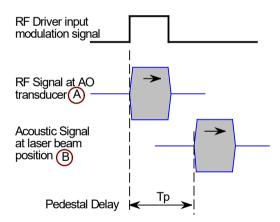

#### Timing and delay considerations

When attempting to synchronize a pulsed laser beam with a pulsed RF acoustic wave in an AO device, the designer must consider the transit time of the acoustic wave from the transducer to the laser beam position. This is called the Pedestal delay.

Input Beam Location

Vertical axis: Place the laser beam at the centre of the active aperture at Ymm above the base. Horizontal (Diffraction) axis: Place beam above the Bragg pivot point.

Timing considerations with respect to the RF modulation signal:

Acousto-optics are travelling wave devices. The acoustic wave is launched from the transducer and travels at velocity V across the laser beam and into the absorber.

1: Pedestal delay = time for the acoustic wavefront to reach the laser beam.

Tp = beam position from transducer (X) / acoustic velocity (V)

2: Transit time = time for the acoustic wavefront to cross the laser beam. Tt = beam diameter (d) / acoustic velocity (V)

Optical switching time for a Gaussian beam is approximately 0.65 x Tt

#### Example:

For the M1431, Quartz AO modulator/deflector, the Bragg pivot point is located at X = 10.5mm from the transducer (+/- 1mm). The Acoustic velocity is 5.7 mm/usec

Thus, for a laser beam placed above the Bragg Pivot point,

Pedestal delay = 1.8 usec

The pedestal delay will depend on the AO model and the actual laser beam position.

For an 8mm input beam diameter,

Transit time = 1.4 usec

(Note: The optical rise time for a Gaussian beam is approximated by 0.65 x transit time)

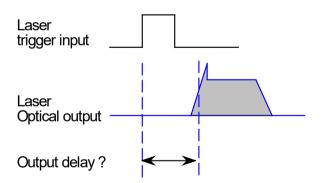

#### Laser synchronization

Please be aware, depending on the Laser type, there may be a significant delay between the laser input trigger signal and the actual laser optical output pulse.

This should be considered when synchronizing the laser and pulsed RF (acoustic) waves.